半導体

半導体とは導体 (電気を良く通す物質) と絶縁体 (電気をほとんど通さない物質) の中間の性質を持つ物質です。また半導体材料を用いたトランジスタやダイオード、それらを多数集積して作られた回路も半導体または半導体チップと呼ばれます。半導体は家電製品から自動車、社会インフラまで世の中で広く使われています。

半導体分野では低消費電力化や高性能化に向け、SiCやGaN等の新材料、新構造のトランジスタ、3次元実装などが注目されています。これらの半導体を安定して製造(歩留り)し、安心して使う(信頼性)為には精度の良い分析技術が不可欠で、それには目的に応じた適切な前処理と分析装置の選択が重要です。このページでは、様々な分析装置と応用例をご紹介いたします。

1. 半導体の検査・解析に貢献するJEOLの装置

2. JEOL半導体関連製品と用途

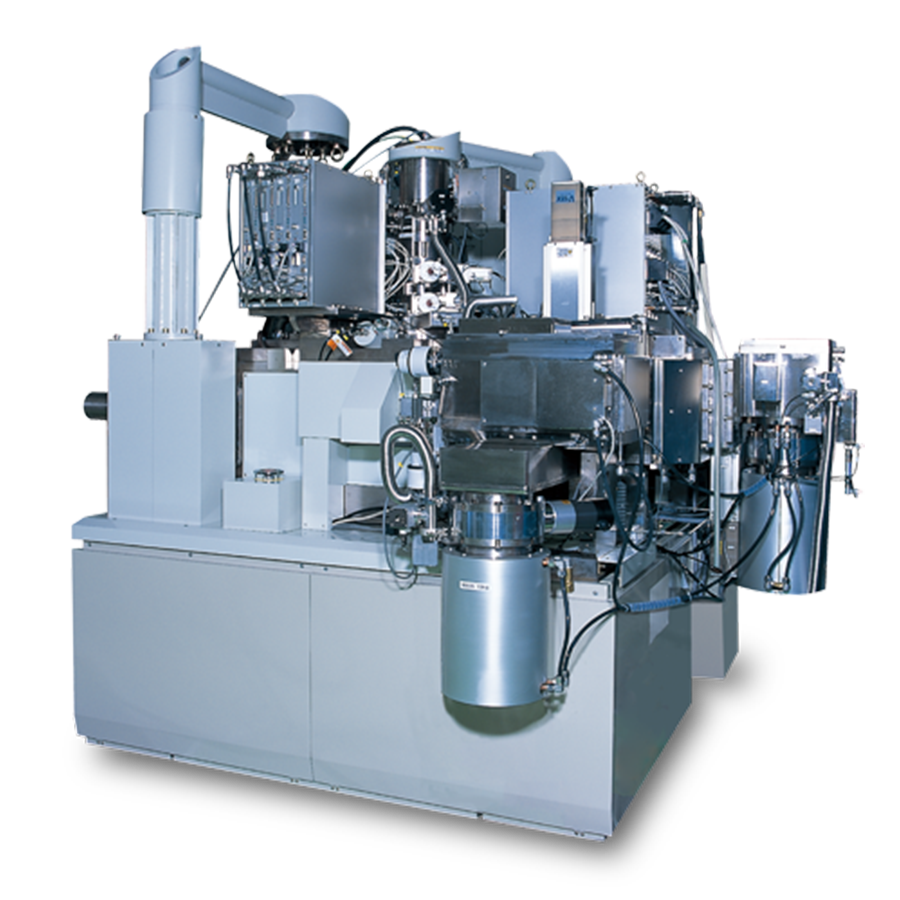

3. EB:電子ビーム描画装置

Electron Beam Lithography System

EB 描画装置は、EDA(Electronic Design Automation)ツール等で設計された集積回路(IC)や各種デバイスの回路データを、電子ビームを用いてガラス基板やウエハ基板上に実存のものとして描き表していく装置です。

日本電子のマスク製作用EB 描画装置は、先端技術で高速、高精度、高信頼性を実現しています。

加速電圧50 kV の可変成形(矩形)ビームとステップ&リピートステージ方式を基本とした描画装置です。

4. FIB-SEM/TEM:先端半導体プロセスにおけるTEM測長の活用

TEMとの連携を容易にする"二軸傾斜カートリッジ"を採用。

カートリッジは、専用のTEM ホルダー / FIB ホルダーにワンタッチで装着します。

TEM グリッドの載せ替え作業から解放されます。

JEM-ACE200F で取得したFinFET (Fin Field-Eff ect Transistor) 型トランジスタのHAADF-STEM 像とフラッシュメモリー のTEM 像の測長例を示します。測長には、システムインフロンティア製のMulti Image Tool を使用しており、測長レシピの作成が可能です。

FinFET型トランジスタのTEM試料作製(FIB-SEM)

FinFET型トランジスタのSE像およびBSE像です。加工終点を見逃さないコントラストの良い鮮明な像を取得できます。

Fin部を狙って正確に薄膜化できています。TEMグリッドの載せ替えなしに、JIB-PS500iからTEMへ試料搬送が可能となり試料破損のリスクを大幅に軽減できます。TEM観察では方位合わせで必須となる2軸傾斜が可能です。

FinFET型トランジスタの構造および組成解析(TEM)

FinFET型トランジスタのHAADF-STEM像とEDSマップです。Finの形状、ゲート周辺の構造、コンタクト部分の配置、および元素分布を観察できます。特に、高分解能HAADF-STEM像では、ゲート絶縁膜 (SiO2やHfO2)やメタルゲートの層構造が鮮明に確認できます。

試料:5 nm FinFET型トランジスタ

加速電圧:200 kV

EDSマップ (ネットカウントマップ)

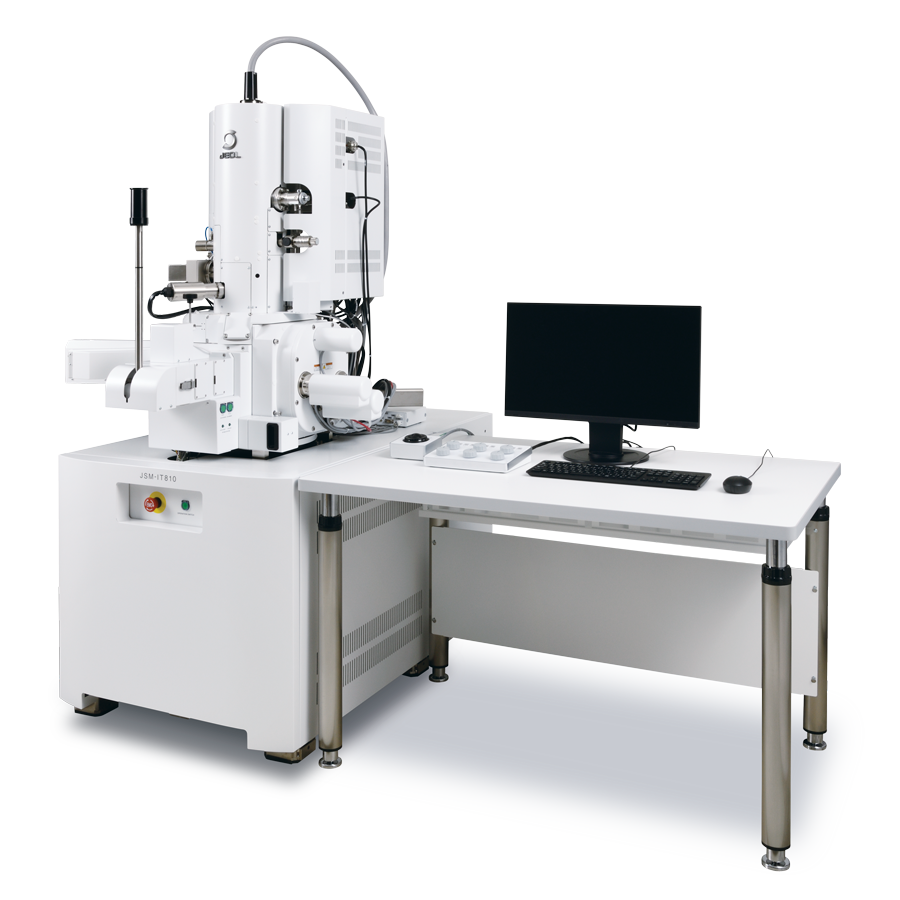

5. SEM:半導体デバイスを観察/分析するためのSEM機能

高分解能SEM では、試料から発生する電子を効率的に検出できる上方検出器を複数搭載しています。低い入射電圧においても レジストパターンやIC 断面の微細な構造や、電位コントラストも明るく観察できます。

レジスト

SRAM

IC 断面

半導体積層チップ (SRAM剥離後) の電位コントラスト観察(SEM)

電位コントラストの概念図

表面観察試料ホルダー

SM-71230SOHD

電位コントラスト (Voltage Contrast: VC) は、半導体デバイス表面の導電性の違いによりSEM像に生じるコントラストです。例えば、タングステンプラグなどに欠陥が生じた場合、欠陥を持つプラグと正常なプラグでは異なるコントラストを示します。これを用いて欠陥の位置を特定することができます。

6. AES/CP:半導体積層チップCP 断面の元素・化学状態別分布の可視化

デバイスの故障解析を行うには断面解析がよく用いられますが、微細化・複雑化するデバイスを分析するためには高空間分解能な分析が求められます。

AES は、バルク試料を高空間分解能かつ高エネルギー分解能で分析可能であるため、より詳細な故障解析が簡便に行えます。ここでは一例として、SRAM のCMOS 領域の元素分布とSi とSiO2

の化学状態別の分布を可視化しました。

SiC パワー半導体ダイオードのpn 接合部の内蔵電位差分析(AES)

pn

接合はデバイスにおける基本構造であり、デバイス動作の重要な役割を担っています。この性能は不純物の量とそのドーピング技術、成膜プロセスに大きく依存します。ボルテージコントラスト(VC)

などで容易に観察することは可能になってきましたが、ドーパント量のわずかな差などをナノメートルオーダーの分解能で詳細に分析する手法は限られます。

AES では、pn 接合部の内蔵電位差をピークのシフト量として評価することが可能です。ここでは、SiC パワー半導体のpn 接合部を分析しました。p 型領域とn 型領域でSi KLL

ピークのピーク位置は1.3 eV 異なっており、このエネルギー差を利用してp 型/n 型の領域の可視化を行いました。

7. アプリケーションノート

YOKOGUSHI (半導体総合)

前工程 物理解析

-

4D-STEMとSTEM-EELSを用いたFinFETのplan-view観察

EM2022-01

-

電子線トモグラフィーによる半導体材料の解析

日本電子news Vol.50 No.6

-

JEM-2500SE:ナノメートル領域解析ツール

-

球面収差補正 TEM (200kV) による半導体デバイス評価

-

TFT液晶パネルコンタクトプラグの断面観察

IB2019-03

-

TEMによる品質管理検査のための試料作製

IB2019-06

-

平面観察と断面観察のためのTEM試料作製

IB2019-07

-

高分解能観察のための高品質TEM試料作製

IB2019-08

前工程 化学分析

-

2種類のGCカラムによるイソプロパノール中不純物の定性分析と比較分析

MSTips No.513

-

msFineAnalysis AIを用いた半導体用溶媒中不純物の定性分析

MSTips No.434

-

GC-MS法によるシリコンウェハ表面からの発生ガス分析

MSTips No.253

-

n型半導体 (Pドープ型) のESRによる測定

ER250001

-

半導体ウェハの欠陥評価 極低温測定の重要性

ER240003

-

材料のESR - 半導体 ① -

ER170006

前工程 電気特性

-

マニュピレーターの応用 ナノプロービングと故障解析

SM2024-01

-

強磁性薄膜とスピン流 (3) - サンプリングの例 -

ER190004

-

材料のESR - 電気検出磁気共鳴 ① -

ER170007

-

材料のESR - 電気検出磁気共鳴 ② -

ER170008

-

材料のESR - 電気検出磁気共鳴 ④ -

ER180001

-

材料のESR - 電気検出磁気共鳴 ⑤ -

ER180002

前工程 リソグラフィー

-

電子ビーム描画装置 JBX-A9の開発

SE2024-01

-

電子ビーム描画装置JBX-8100FSの開発

日本電子news Vol.50 No.9

-

フォトニック結晶レーザ

日本電子 news Vol.46 No.3

-

電子ビーム描画装置JBX-3200MV/JBX-3050MV/JBX-9500FS/JBX-6300FS

後工程 物理解析

半導体のアプリケーションをもっと見る場合は以下のボタンから。